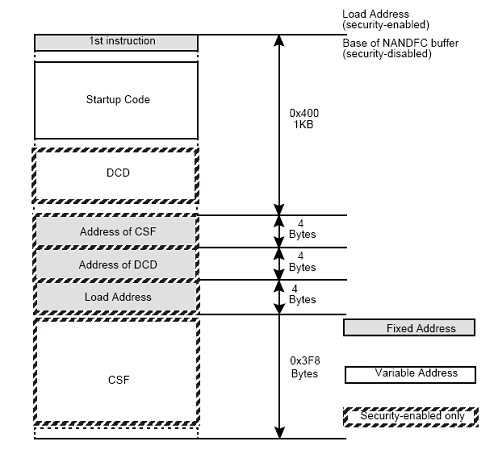

Hi, On our own i.MX27 based boards, we have Micron NAND flash memory (MT29F2G08ABBEAH4). Besides the BI-swapping problem for 2K NAND flashes, I can see that this chip needs an initial reset command before it becomes operational. This is something that has to be done in the early boot code, so before loading the first page of bootloader code (the reset should be sent before the first page of code can be read from flash). From Freescale doc, I found that we have to blow certain fuses to make the i.MX27 boot from internal ROM. According to the document, the ROM code takes care about the initial reset before loading the first page of code from the NAND flash. I’m however a little concerned about this figure in the document :

If I understand well, this should be the structure of the 2K NFC buffer when booting from internal ROM. I don’t think this will be the structure when loading the first page of Barebox code, correct ? Anyone familiar with this Micron specific flash problem ? And the consequences for Barebox ? Do we have to make modifications in the Barebox code to tackle this ? (because the Freescale document is rather WinCE related, I’m not sure this also applies to Barebox/Linux based systems…) I hope we didn’t make a bad choice of NAND flash in combination with i.MX27… ? ;-) Best Regards, Filip (Btw : anyone can tell me what CSF and DCD stand for… ? Did not find any explanations in the i.MX27 reference manual yet) |

_______________________________________________ barebox mailing list barebox@xxxxxxxxxxxxxxxxxxx http://lists.infradead.org/mailman/listinfo/barebox